TSMC เปิดตัวชิป HBM4 Base Dies รุ่นต่อไปที่สร้างขึ้นบนโหนดเทคโนโลยีขนาด 12 nm และ 5 nm

| Share | Tweet |

TSMC เปิดตัวชิป HBM4 Base Dies รุ่นต่อไปที่สร้างขึ้นบนโหนดเทคโนโลยีขนาด 12 nm และ 5 nm

วันนี้ก็มีข่าวจากฝั่ง TSMC ออกมาให้เราได้ชมกันครับกับข่าวของชิป HBM4 Base Dies รุ่นใหม่ในอนาคต โดยในระหว่างการประชุม European Technology Symposium 2024 TSMC ได้ประกาศความพร้อมในกระบวนการผลิตชิป HBM4 รุ่นต่อไปที่ใช้ทั้งโหนดกระบวนการผลิตในเทคโนโลยี 12 นาโนเมตรและ 5 นาโนเมตร ซึ่งการพัฒนาที่สำคัญนี้คาดว่าจะปรับปรุงประสิทธิภาพ การใช้พลังงาน และความหนาแน่นการประมวลผลของหน่วยความจำ HBM4 ได้อย่างมาก ตอบสนองความต้องการของแอปพลิเคชันการประมวลผลประสิทธิภาพสูง (HPC) และปัญญาประดิษฐ์ (AI) การเปลี่ยนจากอินเทอร์เฟซ 1024 บิตแบบดั้งเดิมไปเป็นอินเทอร์เฟซ 2048 บิตแบบ Ultra-wide ถือเป็นลักษณะสำคัญของมาตรฐาน HBM4 รุ่นใหม่ ทำให้การประมวลผลที่เพิ่มขึ้นและประสิทธิภาพที่สูงขึ้นในขณะที่ลดการใช้พลังงาน กระบวนการ N12FFC+ และ N5 ของ TSMC จะถูกใช้ในการผลิตแม่พิมพ์พื้นฐานชิป โดยกระบวนการ N12FFC+ นำเสนอโซลูชันที่คุ้มค่าเพื่อให้ได้ประสิทธิภาพ HBM4 และกระบวนการ N5 ที่ให้การประมวลผลเร็วมากยิ่งขึ้นและลดการใช้พลังงานที่ความเร็ว HBM4 รุ่นใหม่ล่าสุด

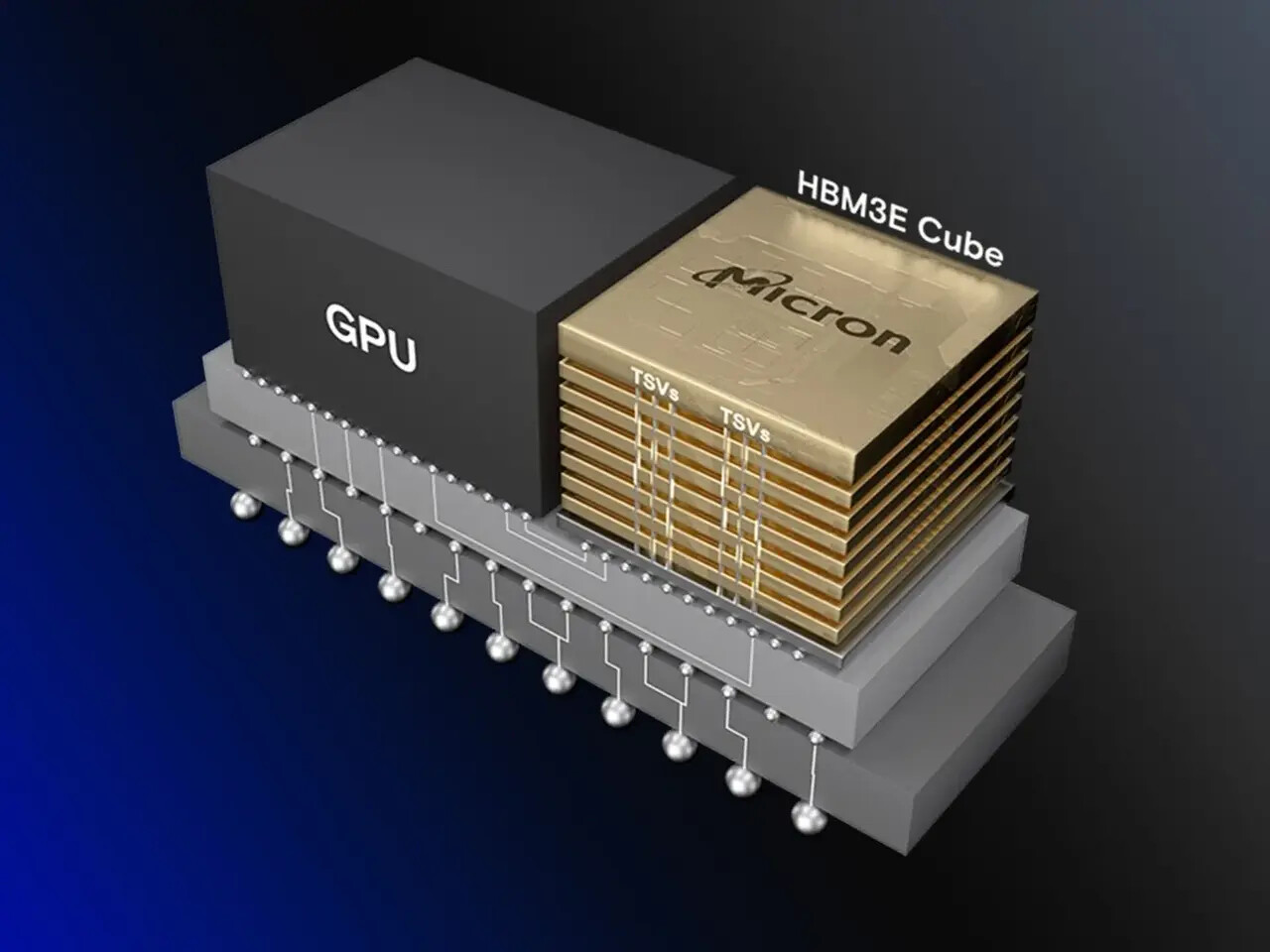

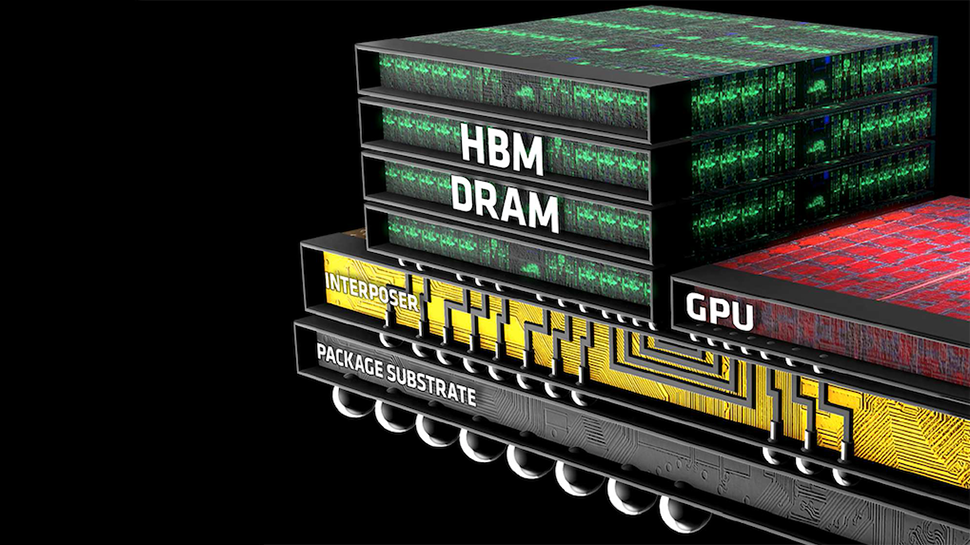

โดยทางบริษัท TSMC กำลังร่วมมือกับพันธมิตรหน่วยความจำ HBM รายใหญ่ รวมถึง Micron, Samsung และ SK Hynix เพื่อรวมโหนดขั้นสูงสำหรับการรวม HBM4 ฟูลสแตก แม่พิมพ์พื้นฐานของ TSMC ซึ่งประดิษฐ์ขึ้นโดยใช้กระบวนการ N12FFC+ จะถูกนำมาใช้เพื่อติดตั้งสแต็กหน่วยความจำ HBM4 บนซิลิคอนอินเตอร์โพเซอร์ควบคู่ไปกับ system-on-chips (SoCs) การตั้งค่านี้จะช่วยให้สามารถสร้างสแต็ก 12-Hi (48 GB) และ 16-Hi (64 GB) โดยมีแบนด์วิดท์ต่อสแต็กเกิน 2 TB/s การทำงานร่วมกันของ TSMC กับพันธมิตร EDA เช่น Cadence, Synopsys และ Ansys ช่วยให้มั่นใจในความสมบูรณ์ของสัญญาณช่อง HBM4 ความแม่นยำด้านความร้อน และการรบกวนทางแม่เหล็กไฟฟ้า (EMI) ในฐาน HBM4 ใหม่ TSMC ยังเพิ่มประสิทธิภาพ CoWoS-L และ CoWoS-R สำหรับการรวม HBM4 ซึ่งหมายความว่าชิปประสิทธิภาพสูงขนาดใหญ่กำลังใช้เทคโนโลยีนี้อยู่แล้ว และเตรียมพร้อมสำหรับการผลิตจำนวนมาก

ที่มา https://www.techpowerup.com/

EN

EN